Parity Checker CMPUT 329 Lab #2 Introduction to Structural VHDL: Parity Checker(1 week)This is an INDIVIDUAL lab. You must complete it by yourself.Updated 26/09/03NOTE: Make sure that all the dip switches(blue box with small white sliding switches) are in the'down' (closest to front of board) position. Otherwisethey may interfere with the proper operation of your design!OverviewIn this lab you will complete the design of a circuit thatcaptures keystrokes from a PS/2 keyboard and converts thekeystrokes to hexadecimal values. The binary representation ofthese values is displayed on the bargraph LED. Another circuitcomputes the parity of the value and displays it on the rightLED of the XStend boardIn order to create this functionality, several independent VHDL componentsmust work together. To aid you in creatingthis design, this lab introduces you to structural VHDL andfamiliarizes you with several other useful concepts in the VHDL design process.BackgroundA parity generator is a circuit that, given an n-1 bit dataword, generates an extra (parity) bit that is transmitted with theword.

The value of this parity bit is determined by the bits of thedata word.In an even parity scheme, the parity bit is a 1 if there is an oddnumber of 1's in the data word. Thus when we examine all the bitstransmitted (data word + parity), we see an even number of ones (thus'even' parity).At the receiving end of the transmission, a parity checker uses thisextra information to detect single-bit errors in the transmitted dataword. It does so by regenerating the parity bit in the same manner asthe generator and comparing the two parity bits. Disagreement betweenthese bits means that one of the transmitted bits is incorrect, thoughthe checker cannot determine which bit is in error. Note thatsingle-bit parity scheme is unable to detect an even number of errors(e.g.

Test Bench for Parity Generator in VHDL library ieee; use ieee.stdlogic1164.all; entity paritygeneratortst is end paritygeneratortst; architecture beh of paritygeneratortst is component paritygenerator port(clk,din, rsta,validin: in stdlogic; validout,parityout: out stdlogic; datao: out stdlogicvector(7 downto 0)); end.

4 bits are wrong).An even parity generator can be implemented by an n-1 input XORcircuit. The XOR of several bits is '1' only when there is an oddnumber of 1's in the source. Our design calculates the parity of afour-bit word. You are responsible for completing a VHDL module toconvert keyboard input into hex values, and creating a VHDL module tocalculate the parity of that hex value and display either a '0' or a'1' on the 7-segment LED on the XStend board.Also, you must display the hex value on the bargraph LED (usingthe rightmost segments) on the XStends board for easyconfirmation of proper kb - hex conversion and paritycalculation.

Segments of this LED should correspond to the bits inthe hex representation of the value. For example, if the value is8, only the most significant LED segment should be lit. Keep inmind that the 7-segment LED and the bargraph LED on the XStendboard are active-low.In order to achieve the above functionality, several components mustbe built. A module to receive and interpret keyboard data is requiredto translate the PS/2 interface. Moreover, another module mustconvert the keyboard data to hexadecimal, and a third must calculatethe parity of this hexadecimal value for output to the LED.Combining these modules into a single design requires a higher-levelVHDL component, which will instantiate the three more basic modules.This higher-level component is written in Structural VHDL.Since this is your first glance at this form of VHDL, you are providedwith an outline of the higher-level file which you must complete.Prelab.

Read the lab assignment and become familiar with what'sinvolved. Also, you may wish to read the section in Wakerly onstructural design (Section 4.7.6). There is more than one way to implement a 4-input XOR functionusing only 2-input XOR gates. Using pencil and paper ( i.e.

Without theFoundation tools), find the implementation that results in the leastnumber of gate delays and the one that incurs the most gate delaysbetween any input and the generation of the output (withoutredundant or superfluous circuitry, or course). Sketch the circuits,and compute the number of gate delays to generate the parity bit ineach case. Write out the equations as VHDL statements, usingbrackets to group the gate inputs, beneath the diagrams. Study the written description of the design below and sketch out ablock diagram of the connections between the components involved. Itis important that you have a good idea about whatoutputs in one component connect to the inputs of another componentbefore you start working with the design tools.LabRecalling the process from Lab 1, create a new project. Next, besure to download the files provided and add them to your project.There are four main files, each representing a VHDL module in thisproject:KBINPUT.vhdDescription:We provide this module for you in a completely functionalform. It will read the input from the keyboard and produceas output a standard PS/2 representation of the key pressed( note this is not the ASCII code of the character.)Input:The global clock (for synchronization), the PS/2 clock anddata lines (from the keyboard) and the global reset signalsare all inputted to this module.

The Sims 4 Career Cheats Getting Promotions and Unlocking Career Items Cheating your Career in The Sims 4 may help you to avoid the repetition of going through the same career track again and again. It's also possible to unlock items in buy mode that are restricted to Sims who have achieved a particular career level. Sims 4 relationship cheat.

( note: thepushbutton switch labelled reset on the board isactive-low. Therefore, when you are using this signal, youmust convert it to active-high.)Output:The keyboard scancode and a keyboard press signal are theoutputs from this module. The scancodecontains the information that you need. Thekeyboard press signallet you know when to read the scancode.

Please examinemodules that we provide you, to find out that there is asimple and standard way of using this signalKBHEX.vhdDescription:This module is provided as a skeleton only, one which youmust complete for yourself. It takes the keyboard scancodeas input and converts it to hexadecimal.

Invalid digitsshould produce no change in the module's output.Input:The scancode and press signals from the KBINPUTmodule are inputted to this module. The press signalfacilitates synchronization of the module (i.e.

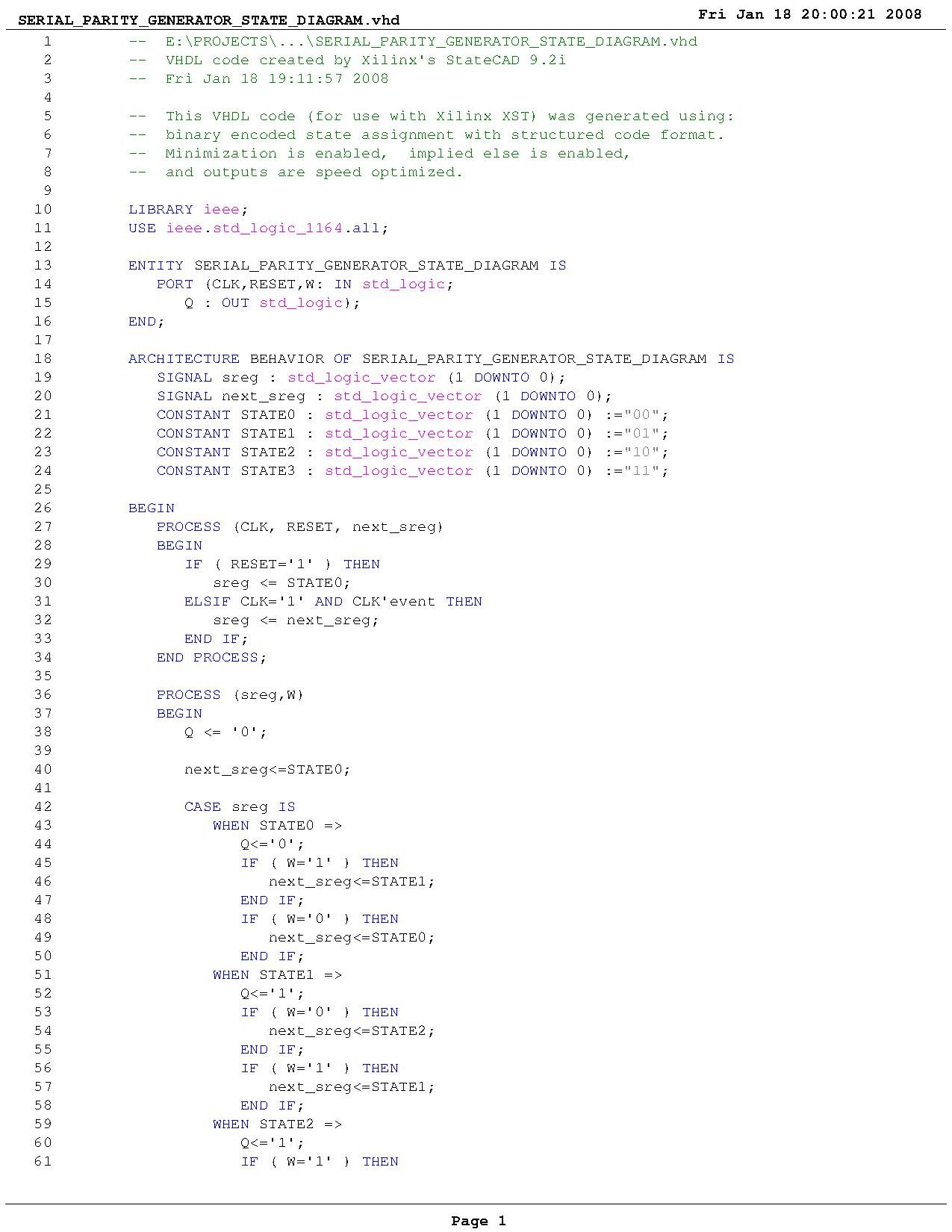

Lets themodule know when to read the scancode)Output:This module outputs the four-bit hexadecimal translation ofthe scancode.PARITY.vhdDescription:You must design this module from scratch. While you mayuse the VHDL wizard to get a start on this module, thebody of the code, which the wizard does notprovide, must be written by you. This module calculatesparity of the hexadecimal input (which is derived fromthe keyboard input) and outputs the parity as it would bedisplayed on the 7-segment LED. Display to the LED iscoded by 7 bits as displayed below:To implement this design, we recommend you use a pair ofin your code. A process is similarto a function in a traditional programming language; theprocess runs whenever a signal in its sensitivity list ischanged.

We recommend that you have one process thatcalculates the parity bit from the incoming hex signaland another that determines the LED output based on thatparity bit.Input:The input to this module is the 4 bit hex value.Output:A 7-bit stdlogicvector, representing the LED output,is outputted from this module.Lab2.vhdDescription:This is a higher level module thatdescribes how the other modules in the design interactwith each other. This description is accomplished inStructural VHDL, and involves declaration andinstantiation of the modules involved. Moreover, whensynthesizing your design, you must ensure that this fileis used as the top level design of your circuit.We have given you most of the information for thisdesign, but you must declare the signals to be used andconnect the components correctly.Input:All inputs to the circuit must be ports in this file.These are the global clock signal, the global reset, andthe PS/2 clock and data signals.Output:Similarly to the inputs, all outputs from the circuitmust be ports in this file. These outputs are the 7-bitLED signal and the 4-bit hexadecimal signal, which issent to the bargraph display.Testing:As a more thorough test of your design, we have provided a VHDLtestbench for this lab, which is used in conjunction with theSonata software.

If you have not used Sonata yet, be sure toread the. The waveformproduced from this testbench is a required part of yoursubmission (add all signals from the testbench to the waveformand save it.)Synthesis:Once all required modules have been created and completed, andthey have been added to your project, you may synthesize yourproject as you did in Lab 1.

Anybody know how to code a parity generator in VHDL? Let's say for example a4-bit generator? Or some other even-bit generator?Use the following function frompackage stdlogicmisc:function XORREDUCE(ARG: STDLOGICVECTOR) return UX01;- Ben Cohen, Raytheon Systems, (310) 334-7389-. 'VHDL Coding Styles and Methodologies, 2nd Edition', Ben Cohen,- ISBN 0-7923-8474-1 Kluwer Academic Publishers, 1999-. 'VHDL Answers to Frequently Asked Questions, 2nd Edition',- Ben Cohen, ISBN 0-7923-8115-7 Kluwer Academic Publishers, 1998- Web page:Em03.03.99 00:00.

Wrote: Anybody know how to code a parity generator in VHDL? Let's say for example a 4-bit generator?

Or some other even-bit generator? Any help would be great.

Thanks, -Steven. you can send replies to this newgroup or to sbutts @Two alternative descriptions:- one uses the well known parity chain. An alternative to this descriptionis a process that contains a FOR LOOP with the XOR operation.- the second has a more behavioural view, it count the numbersof ones.Both result in the same logic (witjh my synthesis tool)Regards,Egbert MolenkampENTITY parity1 ISGENERIC (nbits: positive:= 3);PORT (d: IN bitvector(nbits-1 DOWNTO 0);odd: OUT bit;even: OUT bit);END parity1;ARCHITECTURE xorchain OF parity1 ISSIGNAL chain: bitvector (nbits DOWNTO 0);BEGINchain(nbits). Be careful of using a loop or function call. You do not know how it willsynthesize. It may not matter as what you get may be fast enough.

I tend tobuild my own parity function using parenthases to specify how I want the XORgates structured. This way, I am more likely to get a balanced tree ratherthan a long chain:Good:ODDPARITY. Wrote: Be careful of using a loop or function call. You do not know how it will synthesize. It may not matter as what you get may be fast enough.

I tend to build my own parity function using parenthases to specify how I want the XOR gates structured. This way, I am more likely to get a balanced tree rather than a long chain: Good: ODDPARITY Not so good: ODDPARITY BTW, to get even parity, just add one, better yet, ODDPARITY = EVENPARITYN (not). One more thing, if you have more info on the library of the part you are targeting, you can better optimize the tree. For example, if your ASIC library contained a 3 input XOR gate (some do) then build your tree based on that: Eg.

ODDPARITY Good Luck! PJIs it naive to think that the syntheziser will also figure this out?I mean why should it make a chain if it can make a three, and I thinkit should atleast be smart enough to know how to make large logicfunctionsin 'chucks' that fit the technology-L2C-Lasse Langwadt Christensen, MSEE (to be in 1999)Aalborg University, Department of communication tech.Applied Signal Processing and Implementation (ASPI), mailto:philj.@my-dejanews.com04.03.99 00:00. Let's take Synopsys as an example. It uses a set of rules (constraints) tosynthesize. It scores each solution and uses the 'best' one. There is atrade-off between area and speed.

It typically uses the design that providesthe needed speed with the smallest area. However, for a parity function, atree and a chain both contain the same number of gates and nets, so which isbetter. The tree is faster but if the chain meets your speed requirement, itMAY be used instead of the tree.What will the tool do in a given situation I can't say for sure. Not sureanyone can. I can say that I have done parity checkers and generators andSynopsys DID implement them as chains or poorly structured trees until Iadded the parenthesis to tell it exactly what I wanted. Would what itgenerated have worked? Yes, because it met the speed requirement (and allother constraints).

Is it what I wanted? So, I changed it.Not trying to be difficult here, just trying to point out one of thesubtleties of synthesis.PJIn article,- Posted via Deja News, The Discussion Network -Search, Read, Discuss, or Start Your OwnEm05.03.99 00:00. Wrote: Be careful of using a loop or function call. You do not know how it will synthesize. It may not matter as what you get may be fast enough. I tend to build my own parity function using parenthases to specify how I want the XOR gates structured.

This way, I am more likely to get a balanced tree rather than a long chain: Good: ODDPARITY Not so good: ODDPARITY - If you like a balanced tree like structure AND the number if inputs shouldstill- be generic! You could use the following VHDL description.- It is synthesisable (at least with my synthesis tool).- The solution is NOT mine! (I don't remember the original author)- I only changed it a little to make it synthesiable. My synthesis tool- did not support an 'unconstrained' array in the port declaration, therefore- I added a GENERIC.- Original it was:- entity ParityTree is- port (Inputs: in BitVector;- Output: out Bit);- end ParityTree;- I replaced it with:- entity ParityTree is- generic (nmb: integer);- port (Inputs: in BitVector(1 TO nmb);- Output: out Bit);- end ParityTree;- Have FUN.- Egbert Molenkamp-This example is the VHDL implementation of:- 'To make an n-bit parity generator, take two n/2-bit parity generators- and connect their outputs with an xor gate. A one-bit parity generator- is a piece of wire.' Entity ParityTree isgeneric (nmb: integer);port (Inputs: in BitVector(1 TO nmb);Output: out Bit);end ParityTree;architecture Recursive of ParityTree iscomponent ParityTreegeneric (nmb: integer);port (Inputs: in BitVector (1 TO nmb);Output: out Bit);end component;alias MyInput: BitVector (1 TO Inputs'Length) IS Inputs;signal LowerHalfParity: Bit;signal UpperHalfParity: Bit;signal lower: bitvector(1 TO MyInput'Length/2);signal upper: bitvector(MyInput'Length/2 + 1 TO MyInput'Length);beginGeneralCase:if MyInput'Length 1 generatelower.

Phil jackson writes: What will the tool do in a given situation I can't say for sure. Not sure anyone can. I can say that I have done parity checkers and generators and Synopsys DID implement them as chains or poorly structured trees until I added the parenthesis to tell it exactly what I wanted.

Would what it generated have worked? Yes, because it met the speed requirement (and all other constraints). Is it what I wanted? So, I changed it.I'm curious.

Why did you want precise control over the tree structure,if Synopsys synthesised a working structure already?Is it that you did not/could not enter the real constraints for yourapplication?Curious,- JamieJamie Lokier12.03.99 00:00. I wrote: I'm curious. Why did you want precise control over the tree structure, if Synopsys synthesised a working structure already? Is it that you did not/could not enter the real constraints for your application?I ask because I am interested in techniques for synthesis, and whatreal-life designs require from it.In my mind, adding parantheses wuold not guarantee control over thesynthesised tree structure: just as the tool may convert 'a XOR b XOR cXOR d' into any shape it likes, it has the freedom to implement anythingthat is equivalent to '(a XOR b) XOR (c XOR d)'. That is, it maysynthesise a chain from the latter equation, although it may be lesslikely to find that as its first solution.- JamieRichard Guerin13.03.99 00:00.